Page 446 - DSP Integrated Circuits

P. 446

Problems 43

[32] Wanhammar L., Sikstrom B., Afghahi M., and Pencz J.: A Systematic Bil

Serial Approach to Implement Digital Signal Processing Algorithms, Prot

2nd Nordic Symp. on VLSI in Computers and Communications, Linkopin^

Sweden, June 2-4,1986.

[33] Wanhammar L.: On Algorithms and Architecture Suitable for Digital Signe

Processing, Proc. The European Signal Processing Conf., EUSIPCO - 86, Th

Hague, The Netherlands, Sept. 1986.

[34] Wanhammar L.: Implementation of Wave Digital Filters Using Distribute^

Arithmetic, Signal Processing, Vol. 2, No. 3, pp. 253-260, July 1980.

[35] Wanhammar L.: Implementation of Wave Digital Lattice Filters, Proc. 198<

European Conf. on Circuit Theory and Design, Warsaw, Poland, Sept. 1980.

[36] Wanhammar L.: Implementation of Wave Digital Filters Using Vectoi

Multipliers, Proc. First European Signal Processing Conf., EUSIPCO-8C

Lausanne, Switzerland, pp. 21-26, Sept. 1980.

[37] Wanhammar L.: ATI Approach to LSI Implementation of Wave Digital Filters

Linkoping Studies in Science and Technology, Diss. No. 62, Sweden, Apri

1981.

[38] Wanhammar L., Afghahi M., and Sikstrom B.: On Mapping of Algorithm

onto Hardware, IEEE Intern. Symp. on Circuits and Systems, ISCAS-8£

Espoo, Finland, pp. 1967-1970, June 1988.

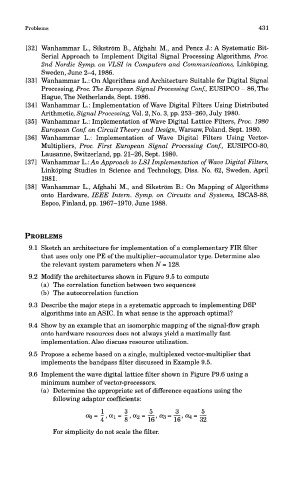

PROBLEMS

9.1 Sketch an architecture for implementation of a complementary FIR filter

that uses only one PE of the multiplier-accumulator type. Determine also

the relevant system parameters when N = 128.

9.2 Modify the architectures shown in Figure 9.5 to compute

(a) The correlation function between two sequences

(b) The autocorrelation function

9.3 Describe the major steps in a systematic approach to implementing DSP

algorithms into an ASIC. In what sense is the approach optimal?

9.4 Show by an example that an isomorphic mapping of the signal-flow graph

onto hardware resources does not always yield a maximally fast

implementation. Also discuss resource utilization.

9.5 Propose a scheme based on a single, multiplexed vector-multiplier that

implements the bandpass filter discussed in Example 9.5.

9.6 Implement the wave digital lattice filter shown in Figure P9.6 using a

minimum number of vector-processors.

(a) Determine the appropriate set of difference equations using the

following adaptor coefficients:

For simplicity do not scale the filter.