Page 448 - DSP Integrated Circuits

P. 448

Problems 433

WHAM. The clock period for the processors is TPE and read and write time for

the memories is TR = TW = TRAM-

(a) Suggest a suitable architecture.

an

(b) How many memories are required, given NPE, WPE, TPE, WRAM, d

n

TRAM> i order to obtain balance between processing capability and

communication bandwidth?

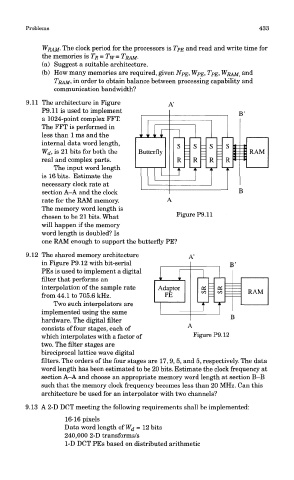

9.11 The architecture in Figure

P9.ll is used to implement

a 1024-point complex FFT.

The FFT is performed in

less than 1 ms and the

internal data word length,

Wd, is 21 bits for both the

real and complex parts.

The input word length

is 16 bits. Estimate the

necessary clock rate at

section A-A and the clock

rate for the RAM memory.

The memory word length is

chosen to be 21 bits. What Figure P9.ll

will happen if the memory

word length is doubled? Is

one RAM enough to support the butterfly PE?

9.12 The shared memory architecture

in Figure P9.12 with bit-serial

PEs is used to implement a digital

filter that performs an

interpolation of the sample rate

from 44.1 to 705.6 kHz.

Two such interpolators are

implemented using the same

hardware. The digital filter

consists of four stages, each of

which interpolates with a factor of Figure P9.12

two. The filter stages are

bireciprocal lattice wave digital

filters. The orders of the four stages are 17, 9, 5, and 5, respectively. The data

word length has been estimated to be 20 bits. Estimate the clock frequency at

section A—A and choose an appropriate memory word length at section B—B

such that the memory clock frequency becomes less than 20 MHz. Can this

architecture be used for an interpolator with two channels?

9.13 A 2-D DCT meeting the following requirements shall be implemented:

16-16 pixels

Data word length of Wj = 12 bits

240,000 2-D transforms/s

1-D DCT PEs based on distributed arithmetic