Page 447 - DSP Integrated Circuits

P. 447

432 Chapter 9 Synthesis of DSP Architectures

(b) Determine the coefficient word

lengths.

(c) How many vector-processors are

required?

(d) How many input signals are

there to the PEs?

9.7 Implement the wave digital lattice

filter discussed in Example 6.5 using

a minimum number of vector-

processors. Can the implementation

be made maximally fast?

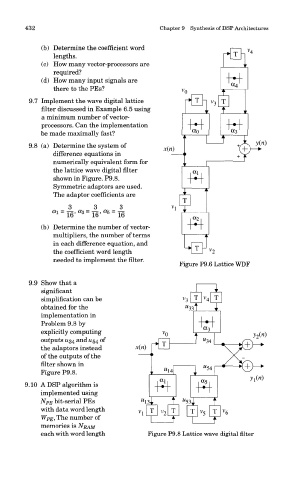

9.8 (a) Determine the system of

difference equations in

numerically equivalent form for

the lattice wave digital filter

shown in Figure. P9.8.

Symmetric adaptors are used.

The adaptor coefficients are

(b) Determine the number of vector-

multipliers, the number of terms

in each difference equation, and

the coefficient word length

needed to implement the filter.

Figure P9.6 Lattice WDF

9.9 Show that a

significant

simplification can be

obtained for the

implementation in

Problem 9.8 by

explicitly computing

outputs z/34 and ^54 of

the adaptors instead

of the outputs of the

filter shown in

Figure P9.8.

9.10 A DSP algorithm is

implemented using

NPE bit-serial PEs

with data word length

WPE, The number of

memories is NRAM

each with word length Figure P9.8 Lattice wave digital filter