Page 444 - DSP Integrated Circuits

P. 444

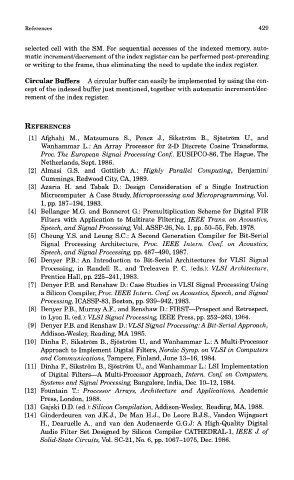

References 429

selected cell with the SM. For sequential accesses of the indexed memory, auto-

matic increment/decrement of the index register can be performed post-prereading

or writing to the frame, thus eliminating the need to update the index register.

Circular Buffers A circular buffer can easily be implemented by using the con-

cept of the indexed buffer just mentioned, together with automatic increment/dec-

rement of the index register.

REFERENCES

[1] Afghahi M., Matsumura S., Pencz J., Sikstrom B., Sjostrom U., and

Wanhammar L.: An Array Processor for 2-D Discrete Cosine Transforms,

Proc. The European Signal Processing Conf., EUSIPCO-86, The Hague, The

Netherlands, Sept. 1986.

[2] Almasi G.S. and Gottlieb A.: Highly Parallel Computing, Benjamin/

Cummings, Redwood City, CA, 1989.

[3] Azaria H. and Tabak D.: Design Consideration of a Single Instruction

Microcomputer A Case Study, Microprocessing and Microprogramming, Vol.

1, pp. 187-194,1983.

[4] Bellanger M.G. and Bonnerot G.: Premultiplication Scheme for Digital FIR

Filters with Application to Multirate Filtering, IEEE Trans, on Acoustics,

Speech, and Signal Processing, Vol. ASSP-26, No. 1, pp. 50-55, Feb. 1978.

[5] Cheung Y.S. and Leung S.C.: A Second Generation Compiler for Bit-Serial

Signal Processing Architecture, Proc. IEEE Intern. Conf. on Acoustics,

Speech, and Signal Processing, pp. 487-490,1987.

[6] Denyer P.B.: An Introduction to Bit-Serial Architectures for VLSI Signal

Processing, in Randell R., and Treleaven P. C. (eds.): VLSI Architecture,

Prentice Hall, pp. 225-241,1983.

[7] Denyer P.B. and Renshaw D.: Case Studies in VLSI Signal Processing Using

a Silicon Compiler, Proc. IEEE Intern. Conf. on Acoustics, Speech, and Signal

Processing, ICASSP-83, Boston, pp. 939-942,1983.

[8] Denyer P.B., Murray A.F., and Renshaw D.: FIRST—Prospect and Retrospect,

in Lyon R. (ed.): VLSI Signal Processing, IEEE Press, pp. 252-263,1984.

[9] Denyer P.B. and Renshaw D.: VLSI Signal Processing: A Bit-Serial Approach,

Addison-Wesley, Reading, MA 1985.

[10] Dinha F, Sikstrom B., Sjostrom U., and Wanhammar L.: A Multi-Processor

Approach to Implement Digital Filters, Nordic Symp. on VLSI in Computers

and Communications, Tampere, Finland, June 13-16,1984.

[11] Dinha F, Sikstrom B., Sjostrom U., and Wanhammar L.: LSI Implementation

of Digital Filters—A Multi-Processor Approach, Intern. Conf. on Computers,

Systems and Signal Processing, Bangalore, India, Dec. 10—12,1984.

[12] Fountain T.: Processor Arrays, Architecture and Applications, Academic

Press, London, 1988.

[13] Gajski D.D. (ed.): Silicon Compilation, Addison-Wesley, Reading, MA, 1988.

[14] Ginderdeuren van J.K.J., De Man H.J., De Loore B.J.S., Vanden Wijngaert

H., Dearuelle A., and van den Audenaerde G.G.J: A High-Quality Digital

Audio Filter Set Designed by Silicon Compiler CATHEDRAL-1, IEEE J. of

Solid-State Circuits, Vol. SC-21, No. 6, pp. 1067-1075, Dec. 1986.