Page 236 - Embedded Microprocessor Systems Real World Design

P. 236

The Microwire and 1% buses described in Chapter 2 can be used for inter-

processor communication, albeit somewhat slowly. In this scheme, one processor

typically controls the bus as a master, and the other responds like a peripheral

device. However, the I'C specification supports multimaster operation in a fairly

unique way.

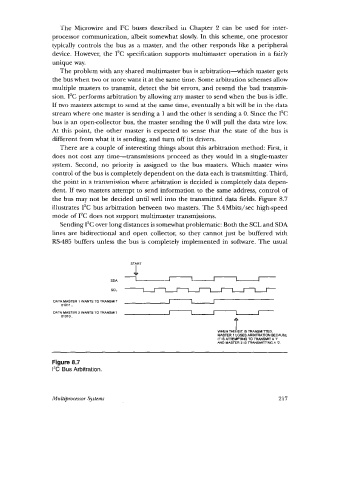

The problem with any shared multimaster bus is arbitration-which master gets

the bus when two or more want it at the same time. Some arbitration schemes allow

multiple masters to transmit, detect the bit errors, and resend the bad transmis

sion. 1% performs arbitration by allowing any master to send when the bus is idle.

If two masters attempt to send at the same time, eventually a bit will be in the data

stream where one master is sending a 1 and the other is sending a 0. Since the 1%

bus is an opencollector bus, the master sending the 0 will pull the data wire low.

At this point, the other master is expected to sense that the state of the bus is

different from what it is sending, and turn off its drivers.

There are a couple of interesting things about this arbitration method: First, it

does not cost any time-transmissions proceed as they would in a single-master

system. Second, no priority is assigned to the bus masters. Which master wins

control of the bus is completely dependent on the data each is transmitting. Third,

the point in a transmission where arbitration is decided is completely data depen-

dent. If two masters attempt to send information to the same address, control of

the bus may not be decided until well into the transmitted data fields. Figure 8.7

illustrates 1% bus arbitration between two masters. The 3.4Mbits/sec high-speed

mode of 1% does not support multimaster transmissions.

Sending 1% over long distances is somewhat problematic: Both the SCL and SDA

lines are bidirectional and open collector, so they cannot just be buffered with

RS-485 buffers unless the bus is completely implemented in software. The usual

SCL

DATA MASTER I WANTS TO TRANSMIT I

0101 1

DATA MASTER 2 WANTS TO TRANSMIT

01010

f

WHEN THIS! BIT IS TRANSMITED,

MASTER 1 LOSES ARBITRATION BECAUSE

IT IS ATTEMPTING TO TRANSMIT A '1'

AND MASTER 2 IS TRANSMlmNG A 'W

Figure 8.7

1% Bus Arbitration.

Multi#n-ocessor Systems 217