Page 79 - Embedded Microprocessor Systems Real World Design

P. 79

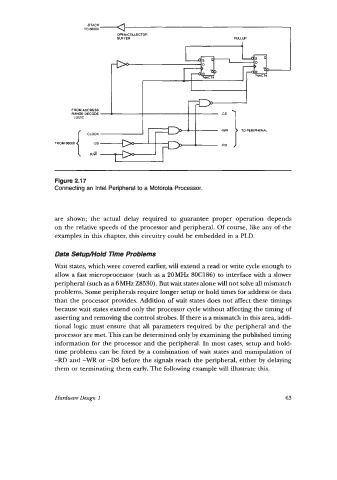

-DTACK A

TO 88ooO

OPENCOLLECTOR

BUFFER PULLUP

FROM ADDRESS

RANGE DECODE

LOGIC

CLOCK

FROM WOW

Figure 2.17

Connecting an Intel Peripheral to a Motorola Processor.

are shown; the actual delay required to guarantee proper operation depends

on the relative speeds of the processor and peripheral. Of course, like any of the

examples in this chapter, this circuitry could be embedded in a PLD.

Data SetupAioId Time Problems

Wait states, which were covered earlier, will extend a read or write cycle enough to

allow a fast microprocessor (such as a 20MHz 80Cl86) to interface with a slower

peripheral (such as a 6MHz 28530). But wait states alone will not solve all mismatch

problems. Some peripherals require longer setup or hold times for address or data

than the processor provides. Addition of wait states does not affect these timings

because wait states extend only the processor cycle without affecting the timing of

asserting and removing the control strobes. If there is a mismatch in this area, addi-

tional logic must ensure that all parameters required by the peripheral and the

processor are met. This can be determined only by examining the published timing

information for the processor and the peripheral. In most cases, setup and hold-

time problems can be fixed by a combination of wait states and manipulation of

-RD and -WR or -DS before the signals reach the peripheral, either by delaying

them or terminating them early. The following example will illustrate this.

Hardware Design 1 63