Page 80 - Embedded Microprocessor Systems Real World Design

P. 80

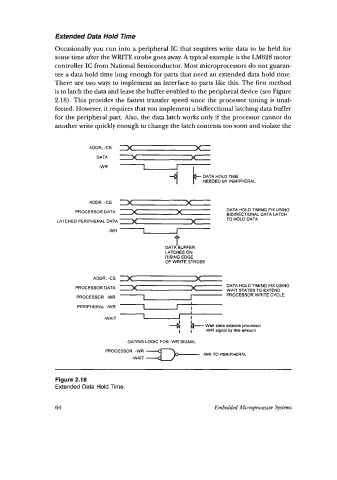

Extended Data Hold Time

Occasionally you run into a peripheral IC that requires write data to be held for

some time after the WRITE strobe goes away. A typical example is the LM628 motor

controller IC from National Semiconductor. Most microprocessors do not guaran-

tee a data hold time long enough for parts that need an extended data hold time.

There are two ways to implement an interface to parts like this. The first method

is to latch the data and leave the buffer enabled to the peripheral device (see Figure

2.18). This provides the fastest transfer speed since the processor timing is unaf-

fected. However, it requires that you implement a bidirectional latching data buffer

for the peripheral part. Also, the data latch works only if the processor cannot do

another write quickly enough to change the latch contents too soon and violate the

ADDR. -CS '-Xp)

DATA * X X - '

-WR 1 DATA HOLD TIME

-WR -

NEEDED BY PERIPHERAL

ADDR. -CS =-x-'

PROCESSOR DATA X X - DATA HOLD TIMING FIX USING

BIDIRECTIONAL DATA LATCH

LATCHED PERIPHERAL DATA X X - TO HOLD DATA

f

DATABUFFER

LATCHES ON

RISING EDGE

OF WRITE STROBE

ADDR, -CS

DATA HOLD TIMING FIX USING

PROCESSOR DATA WAIT STATES TO EXTEND

PROCESSOR WRITE CYCLE

PROCESSOR -WR

PERIPHERAL -WR

-WAIT

4 &- Wa% state exlends processor

I I -WR signal by this amount

GATING LOGIC FOR -WR SIGNAL

PROCESSOR -WR

-WR TO PERIPHERAL

-WAIT

Figure 2.18

Extended Data Hold Time.

64 Embedded Micr@rocessm Systems