Page 284 - Engineering Digital Design

P. 284

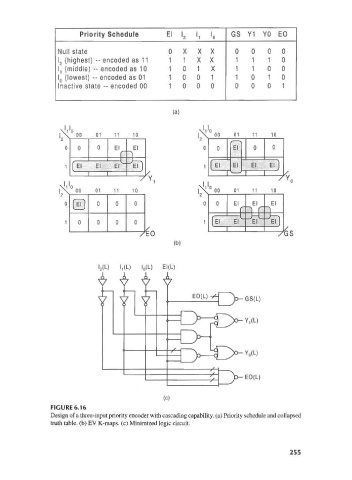

Priority Schedule El "2 "l "o GS Y1 YO EO

Null state 0 X X X 0 0 0 0

I 2 (highest) -- encoded as 11 1 1 X X 1 1 1 0

I, (middle) -- encoded as 10 1 0 1 X 1 1 0 0

I 0 (lowest) -- encoded as 01 1 0 0 1 1 0 1 0

Inactive state -- encoded 00 1 0 0 0 0 0 0 1

(a)

vro vi'o

|\ 00 01 11 10 |\ 00 01 11 10

<L

0 0 0 El El 0 El 0 0

1 El El •^1 [EI El El

(£_

N[I 0 01 11 10 |\ ° 00 01 11 10

NV' 00

'2 N

0 (IT) 0 0 0 0 0 El El El

^*"~ — v "*™*\

(a J

1 0 0 0 0 El bl E,J

(b)

I 2(L) I^L) I 0(L) EI(L)

EO(L)

Y ~\-GS(L)

'i(D

(c)

FIGURE 6.16

Design of a three-input priority encoder with cascading capability, (a) Priority schedule and collapsed

truth table, (b) EV K-maps. (c) Minimized logic circuit.

255