Page 379 - Engineering Digital Design

P. 379

350 CHAPTER 8 / ARITHMETIC DEVICES AND ARITHMETIC LOGIC UNITS (ALUs)

011 1

st

101 0 B ^ Three operands for 1 CS sum

111 1

001 0

1 nd

111 1 C n )> Three operands for 2 CS sum

101 1

, .j.^ operands for final sum

2 1

101 0 C = Final CS carries, C

10101 1 SUM, S

(a)

A 3 B 3 C 3 A 2 B 2 C 2 A 1 B 1 C 1 A 0 B 0 C 0

(H) (H) (H) (H) (H) (H) (H) (H) (H) (H) (H) (H)

S 5(H) S 4(H) S 3(H) S 2(H) S^H) S 0(H)

(b)

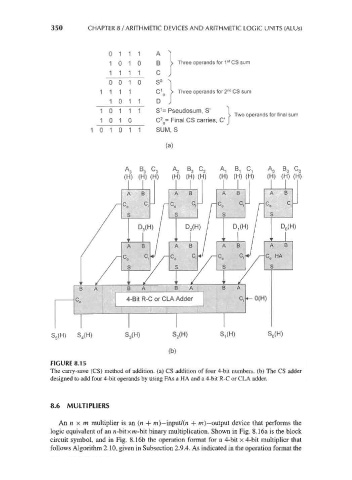

FIGURE 8.15

The carry-save (CS) method of addition, (a) CS addition of four 4-bit numbers, (b) The CS adder

designed to add four 4-bit operands by using FAs a HA and a 4-bit R-C or CLA adder.

8.6 MULTIPLIERS

An n x m multiplier is an (n + w)—input/(n + m)—output device that performs the

logic equivalent of an n-bitxw-bit binary multiplication. Shown in Fig. 8.16a is the block

circuit symbol, and in Fig. 8.16b the operation format for a 4-bit x 4-bit multiplier that

follows Algorithm 2.10, given in Subsection 2.9.4. As indicated in the operation format the