Page 382 - Engineering Digital Design

P. 382

8.7 PARALLEL DIVIDERS 353

oo

P P P r P r P P r r P r P

r

r

7 ~6 5 4 3 2 1 0

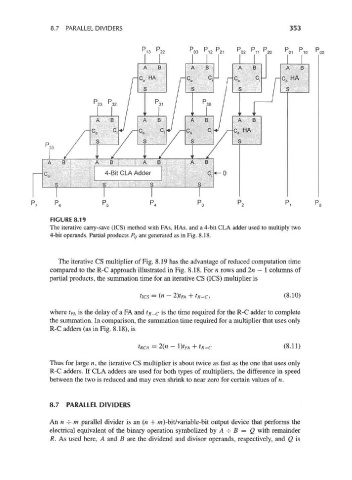

FIGURE 8.19

The iterative carry-save (ICS) method with FAs, HAs, and a 4-bit CLA adder used to multiply two

4-bit operands. Partial products P,j are generated as in Fig. 8.18.

The iterative CS multiplier of Fig. 8.19 has the advantage of reduced computation time

compared to the R-C approach illustrated in Fig. 8.18. For n rows and 2n — 1 columns of

partial products, the summation time for an iterative CS (ICS) multiplier is

tics = (n- 2}t FA + t R^ c, (8.10)

where tp A is the delay of a FA and t R- C is the time required for the R-C adder to complete

the summation. In comparison, the summation time required for a multiplier that uses only

R-C adders (as in Fig. 8.18), is

tRCA = 2(n - l)t FA + tR-c (8.11)

Thus for large n, the iterative CS multiplier is about twice as fast as the one that uses only

R-C adders. If CLA adders are used for both types of multipliers, the difference in speed

between the two is reduced and may even shrink to near zero for certain values of n.

8.7 PARALLEL DIVIDERS

An n -=r m parallel divider is an (n + m)-bit/variable-bit output device that performs the

electrical equivalent of the binary operation symbolized by A -r B = Q with remainder

R. As used here, A and B are, the dividend and divisor operands, respectively, and Q is