Page 686 - Engineering Digital Design

P. 686

(b)

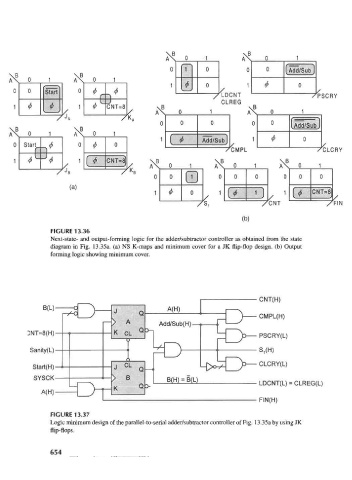

FIGURE 13.36

Next-state- and output-forming logic for the adder/subtractor controller as obtained from the state

diagram in Fig. 13.35a. (a) NS K-maps and minimum cover for a JK flip-flop design, (b) Output

forming logic showing minimum cover.

CNT(H)

B(L)-

X ^M I ** f\ _ _ * _ ' i_ \

CMPL(H)

|~y A _ Add/Sub(H)—^ 1 ' /

CNT=8(H)-

Sanity(L) -M \ J pq J ^ 1 S^H)

Start(H) -i-j HJ CL O |J H>-^O^~ CL RY(L)

°

SYSCK-

LDCNT(L) = CLREG(L)

FIN(H)

FIGURE 13.37

Logic minimum design of the parallel-to-serial adder/subtractor controller of Fig. 13.35a by using JK

flip-flops.

654