Page 71 - System on Package_ Miniaturization of the Entire System

P. 71

48 Cha pte r T w o

Code Security

4 Kw

128 Kw sectored 18 Kw boot Event manager

flash RAM

RAM A

Event manager

B

XINTF

Memory bus

12-bit ADC

Watchdog

Interrupt management

GPI0

Peripheral bus

150-MIPS C28x TM 32-bit DSP

32 × 32-bit

multiplier R-M-W McBSP

Atomic

ALU

CAN 2.0B

32-bit

timers (3)

32-bit SCI (UART) A

Register

Real time file

JTAG SCI (UART) B

SPI

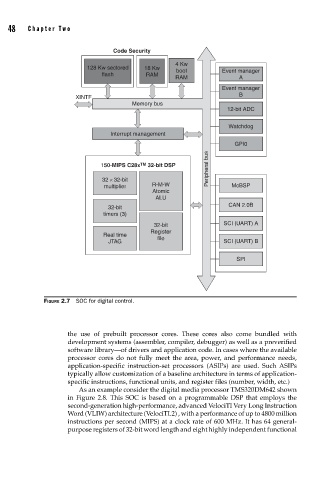

FIGURE 2.7 SOC for digital control.

the use of prebuilt processor cores. These cores also come bundled with

development systems (assembler, compiler, debugger) as well as a preverified

software library—of drivers and application code. In cases where the available

processor cores do not fully meet the area, power, and performance needs,

application-specific instruction-set processors (ASIPs) are used. Such ASIPs

typically allow customization of a baseline architecture in terms of application-

specific instructions, functional units, and register files (number, width, etc.)

As an example consider the digital media processor TMS320DM642 shown

in Figure 2.8. This SOC is based on a programmable DSP that employs the

second-generation high-performance, advanced VelociTI Very Long Instruction

Word (VLIW) architecture (VelociTI.2) , with a performance of up to 4800 million

instructions per second (MIPS) at a clock rate of 600 MHz. It has 64 general-

purpose registers of 32-bit word length and eight highly independent functional