Page 70 - System on Package_ Miniaturization of the Entire System

P. 70

Intr oduction to System-on-Chip (SOC) 47

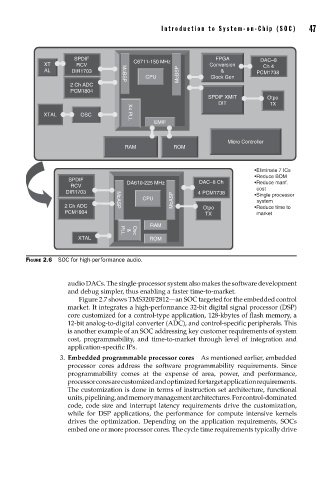

SPDIF FPGA DAC–8

XT RCV C6711-150 MHz Conversion Ch 4

AL DIR1703 & PCM1738

CPU McBSP Clock Gen

McBSP

2 Ch ADC

PCM1804

SPDIF XMIT Otpo

DIT TX

XTAL OSC X4 PLL

EMIF

Micro Controller

RAM ROM

•Eliminate 7 ICs

•Reduce BOM

SPDIF DA610-225 MHz DAC–8 Ch •Reduce manf.

RCV cost

DIR1703 4 PCM1738 •Single processor

CPU McASP system

2 Ch ADC Otpo •Reduce time to

McASP

PCM1804

TX market

RAM

XTAL PLL & Osc ROM

FIGURE 2.6 SOC for high-performance audio.

audio DACs. The single-processor system also makes the software development

and debug simpler, thus enabling a faster time-to-market.

Figure 2.7 shows TMS320F2812—an SOC targeted for the embedded control

market. It integrates a high-performance 32-bit digital signal processor (DSP)

core customized for a control-type application, 128-kbytes of flash memory, a

12-bit analog-to-digital converter (ADC), and control-specific peripherals. This

is another example of an SOC addressing key customer requirements of system

cost, programmability, and time-to-market through level of integration and

application-specific IPs.

3. Embedded programmable processor cores As mentioned earlier, embedded

processor cores address the software programmability requirements. Since

programmability comes at the expense of area, power, and performance,

processor cores are customized and optimized for target application requirements.

The customization is done in terms of instruction set architecture, functional

units, pipelining, and memory management architectures. For control-dominated

code, code size and interrupt latency requirements drive the customization,

while for DSP applications, the performance for compute intensive kernels

drives the optimization. Depending on the application requirements, SOCs

embed one or more processor cores. The cycle time requirements typically drive