Page 72 - System on Package_ Miniaturization of the Entire System

P. 72

Intr oduction to System-on-Chip (SOC) 49

TMS320DM642

Video

Port-0

L1P Cache Video

16 kbytes Video

Port-1

TMS320C64x TM Enhanced DMA Controller Port-2

DSP core L2 Cache/Memory 256 KBytes McASP

10/100

mac

L1D Cache ethernet

16 kbytes

66 MHz PCI

t i i

EMIF

64-bit wide @ 133 MHz

SDRAM

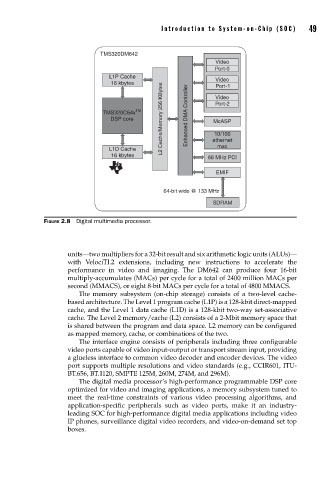

FIGURE 2.8 Digital multimedia processor.

units—two multipliers for a 32-bit result and six arithmetic logic units (ALUs)—

with VelociTI.2 extensions, including new instructions to accelerate the

performance in video and imaging. The DM642 can produce four 16-bit

multiply-accumulates (MACs) per cycle for a total of 2400 million MACs per

second (MMACS), or eight 8-bit MACs per cycle for a total of 4800 MMACS.

The memory subsystem (on-chip storage) consists of a two-level cache-

based architecture. The Level 1 program cache (L1P) is a 128-kbit direct-mapped

cache, and the Level 1 data cache (L1D) is a 128-kbit two-way set-associative

cache. The Level 2 memory/cache (L2) consists of a 2-Mbit memory space that

is shared between the program and data space. L2 memory can be configured

as mapped memory, cache, or combinations of the two.

The interface engine consists of peripherals including three configurable

video ports capable of video input-output or transport stream input, providing

a glueless interface to common video decoder and encoder devices. The video

port supports multiple resolutions and video standards (e.g., CCIR601, ITU-

BT.656, BT.1120, SMPTE 125M, 260M, 274M, and 296M).

The digital media processor’s high-performance programmable DSP core

optimized for video and imaging applications, a memory subsystem tuned to

meet the real-time constraints of various video processing algorithms, and

application-specific peripherals such as video ports, make it an industry-

leading SOC for high-performance digital media applications including video

IP phones, surveillance digital video recorders, and video-on-demand set top

boxes.