Page 81 - System on Package_ Miniaturization of the Entire System

P. 81

System-

RTL/ISS HW

Functional/

Executable

Level

-SW Cosimulation

Behavioral

Cosimulation

HW-SW Cosimulation

Spec.

-SW Cosimulation

Custom

logic

C assembly/

Compile code for target

coding

Verification

SW requirements

Regression

SW architecture

processor

SW integration

Subsystem

integration

Reusable

modules

Requirements & Specifications

HW/SW partitioning & tradeoffs

System architecture design

Application

assembly

Drivers

module

specific

in C/

SW

IP Respository

Chip-level

Subsystem-level

Formal verification

Functional verification

Physical design

Synthesis

Peripherals

DSP cores

Processor/

Bridges

Controllers

Memories

DFT

HW

Reusable HW/SW Simulation/Verification Tech libraries Profiling and optimization Simulation Gate-level/SPICE PG HW/SW integration & test Product

modules

Subsystem

Integration

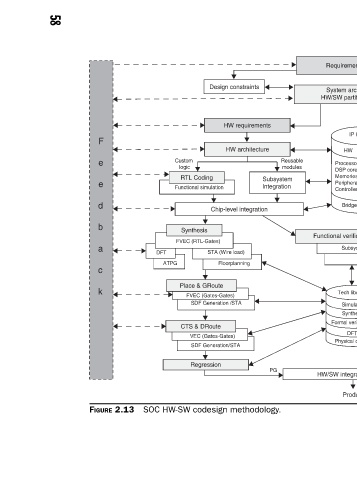

Design constraints HW requirements HW architecture Chip-level integration STA (Wire load) Floorplanning FVEC (Gates-Gates) SDF Generation /STA VEC (Gates-Gates) SDF Generation/STA SOC HW-SW codesign methodology.

Custom logic RTL Coding Functional simulation Synthesis FVEC (RTL-Gates) Place & GRoute CTS & DRoute Regression

ATPG

DFT

FIGURE 2.13

F e e d b a c k

58