Page 331 - A Practical Guide from Design Planning to Manufacturing

P. 331

Semiconductor Manufacturing 301

costs in the billions of dollars and still growing, there are increasingly

few companies that can afford to take this type of risk.

Part of the risk is that semiconductor products are worthless without

software. Processors are only useful for running programs. The future

demand for processors and other semiconductor products depends

greatly on what software is in demand. Processors are like cars that can

go anywhere there are roads, but it is up to the software industry to build

the roads to new destinations consumers actually want to visit. Continued

investment by the semiconductor industry to drive Moore’s law only

makes financial sense if the software industry continues to find new ways

of making use of new hardware capabilities. It is a huge leap of faith by

the hardware industry to believe that providing more processing power,

memory capacity, network bandwidth, and other hardware improvements

will allow the creation of software with sufficient demand to pay for the

costs of developing these capabilities (in addition to some profit).

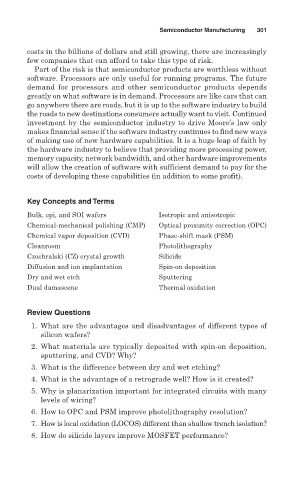

Key Concepts and Terms

Bulk, epi, and SOI wafers Isotropic and anisotropic

Chemical-mechanical polishing (CMP) Optical proximity correction (OPC)

Chemical vapor deposition (CVD) Phase-shift mask (PSM)

Cleanroom Photolithography

Czochralski (CZ) crystal growth Silicide

Diffusion and ion implantation Spin-on deposition

Dry and wet etch Sputtering

Dual damascene Thermal oxidation

Review Questions

1. What are the advantages and disadvantages of different types of

silicon wafers?

2. What materials are typically deposited with spin-on deposition,

sputtering, and CVD? Why?

3. What is the difference between dry and wet etching?

4. What is the advantage of a retrograde well? How is it created?

5. Why is planarization important for integrated circuits with many

levels of wiring?

6. How to OPC and PSM improve photolithography resolution?

7. How is local oxidation (LOCOS) different than shallow trench isolation?

8. How do silicide layers improve MOSFET performance?