Page 168 - Bebop to The Boolean Boogie An Unconventional Guide to Electronics Fundamentals, Components, and Processes

P. 168

Integrated Circuits (ICs) 149

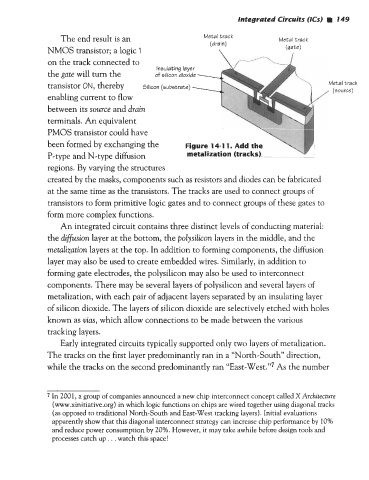

The end result is an Metal track Metal track

NMOS transistor; a logic 1

on the track connected to

the gate will turn the of silicon dioxide

transistor ON, thereby ~i~icon (substrate) Metal track

enabling current to flow / (source)

between its source and drain I

terminals. An equivalent /

PMOS transistor could have

been formed by exchanging the Figure 14-1 1 I

P-type and N-type diffusion metalization (tracks)

regions. By varying the structures

created by the masks, components such as resistors and diodes can be fabricated

at the same time as the transistors. The tracks are used to connect groups of

transistors to form primitive logic gates and to connect groups of these gates to

form more complex functions.

An integrated circuit contains three distinct levels of conducting material:

the diffusion layer at the bottom, the polysilicon layers in the middle, and the

metalimion layers at the top. In addition to forming components, the diffusion

layer may also be used to create embedded wires. Similarly, in addition to

forming gate electrodes, the polysilicon may also be used to interconnect

components. There may be several layers of polysilicon and several layers of

metalization, with each pair of adjacent layers separated by an insulating layer

of silicon dioxide. The layers of silicon dioxide are selectively etched with holes

known as vias, which allow connections to be made between the various

tracking layers.

Early integrated circuits typically supported only two layers of metalization.

The tracks on the first layer predominantly ran in a “North-South” direction,

As

while the tracks on the second predominantly ran “Ea~t-West.”~ the number

7 In 2001, a group of companies announced a new chip interconnect concept called X Architecture

(www.xinitiative.org) in which logic functions on chips are wired together using diagonal tracks

(as opposed to traditional North-South and East-West tracking layers). Initial evaluations

apparently show that this diagonal interconnect strategy can increase chip performance by 10%

and reduce power consumption by 20%. However, it may take awhile before design tools and

processes catch up. . . watch this space!