Page 425 - DSP Integrated Circuits

P. 425

410 Chapter 9 Synthesis of DSP Architectures

9.7 BUILDING LARGE DSP SYSTEMS

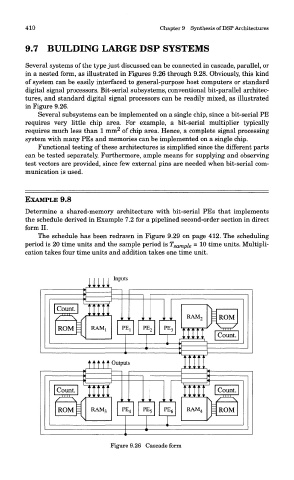

Several systems of the type just discussed can be connected in cascade, parallel, or

in a nested form, as illustrated in Figures 9.26 through 9.28. Obviously, this kind

of system can be easily interfaced to general-purpose host computers or standard

digital signal processors. Bit-serial subsystems, conventional bit-parallel architec-

tures, and standard digital signal processors can be readily mixed, as illustrated

in Figure 9.26.

Several subsystems can be implemented on a single chip, since a bit-serial PE

requires very little chip area. For example, a bit-serial multiplier typically

2

requires much less than 1 mm of chip area. Hence, a complete signal processing

system with many PEs and memories can be implemented on a single chip.

Functional testing of these architectures is simplified since the different parts

can be tested separately. Furthermore, ample means for supplying and observing

test vectors are provided, since few external pins are needed when bit-serial com-

munication is used.

EXAMPLE 9.8

Determine a shared-memory architecture with bit-serial PEs that implements

the schedule derived in Example 7.2 for a pipelined second-order section in direct

form II.

The schedule has been redrawn in Figure 9.29 on page 412. The scheduling

period is 20 time units and the sample period is T sampi e = 10 time units. Multipli-

cation takes four time units and addition takes one time unit.

Figure 9.26 Cascade form