Page 430 - DSP Integrated Circuits

P. 430

9.9 FFT Processor, Cont. 415

This selection is described by the following constraints:

The variables with indices 0 to N/2, - 1 are assigned to RAMo and the rest

toRAMi.

Butterflies 0 to AT/4 - 1 are assigned to PEo and the rest to PEi.

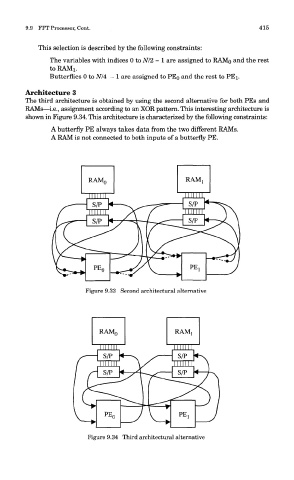

Architecture 3

The third architecture is obtained by using the second alternative for both PEs and

RAMs—i.e., assignment according to an XOR pattern. This interesting architecture is

shown in Figure 9.34. This architecture is characterized by the following constraints:

A butterfly PE always takes data from the two different RAMs.

A RAM is not connected to both inputs of a butterfly PE.

Figure 9.33 Second architectural alternative

Figure 9.34 Third architectural alternative