Page 465 - DSP Integrated Circuits

P. 465

450 Chapter 10 Digital Systems

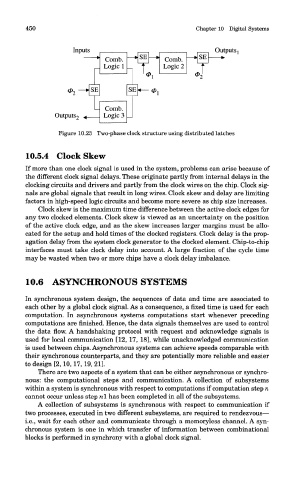

Figure 10.23 Two-phase clock structure using distributed latches

10.5.4 Clock Skew

If more than one clock signal is used in the system, problems can arise because of

the different clock signal delays. These originate partly from internal delays in the

clocking circuits and drivers and partly from the clock wires on the chip. Clock sig-

nals are global signals that result in long wires. Clock skew and delay are limiting

factors in high-speed logic circuits and become more severe as chip size increases.

Clock skew is the maximum time difference between the active clock edges for

any two clocked elements. Clock skew is viewed as an uncertainty on the position

of the active clock edge, and as the skew increases larger margins must be allo-

cated for the setup and hold times of the clocked registers. Clock delay is the prop-

agation delay from the system clock generator to the clocked element. Chip-to-chip

interfaces must take clock delay into account. A large fraction of the cycle time

may be wasted when two or more chips have a clock delay imbalance.

10.6 ASYNCHRONOUS SYSTEMS

In synchronous system design, the sequences of data and time are associated to

each other by a global clock signal. As a consequence, a fixed time is used for each

computation. In asynchronous systems computations start whenever preceding

computations are finished. Hence, the data signals themselves are used to control

the data flow. A handshaking protocol with request and acknowledge signals is

used for local communication [12, 17, 18], while unacknowledged communication

is used between chips. Asynchronous systems can achieve speeds comparable with

their synchronous counterparts, and they are potentially more reliable and easier

to design [2,10,17,19, 21].

There are two aspects of a system that can be either asynchronous or synchro-

nous: the computational steps and communication. A collection of subsystems

within a system is synchronous with respect to computations if computation step n

cannot occur unless step nl has been completed in all of the subsystems.

A collection of subsystems is synchronous with respect to communication if

two processes, executed in two different subsystems, are required to rendezvous—

i.e., wait for each other and communicate through a memoryless channel. A syn-

chronous system is one in which transfer of information between combinational

blocks is performed in synchrony with a global clock signal.