Page 315 - Engineering Digital Design

P. 315

286 CHAPTER 6 / NONARITHMETIC COMBINATIONAL LOGIC DEVICES

begin

return((and_table)(l,r));

end "and";

architecture example of and_operation is

signal Y,A,B: std_logic_1164;

begin

Y <= A and B;

end example;

Here, std_logic_1164 refers to an IEEE standard logic package within which UX01 is a

subtype for 4-valued logic systems. Thus, the operation "and" takes on the new meaning

"and_table" contained in the standard package. Also, 1 and r (in line 1) are two of a class of

value kind attributes that return the leftmost element index (1) or rightmost element index

(r) of a given type or subtype.

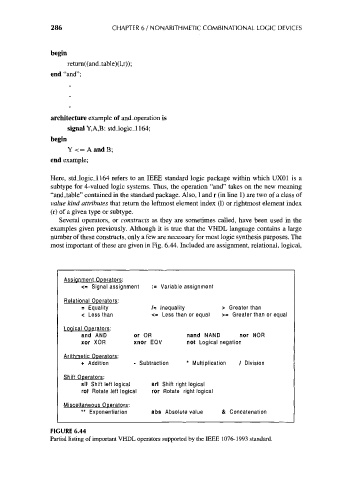

Several operators, or constructs as they are sometimes called, have been used in the

examples given previously. Although it is true that the VHDL language contains a large

number of these constructs, only a few are necessary for most logic synthesis purposes. The

most important of these are given in Fig. 6.44. Included are assignment, relational, logical,

Assignment Operators:

<= Signal assignment := Variable assignment

Relational Operators:

= Equality /= Inequality > Greater than

< Less than <= Less than or equal >= Greater than or equal

Logical Operators:

and AND or OR nand NAND nor NOR

xor XOR xnor EQV not Logical negation

Arithmetic Operators:

+ Addition - Subtraction * Multiplication / Division

Shift Operators:

sll Shift left logical srl Shift right logical

rol Rotate left logical ror Rotate right logical

Miscellaneous Operators:

** Exponentiation abs Absolute value & Concatenation

FIGURE 6.44

Partial listing of important VHDL operators supported by the IEEE 1076-1993 standard.