Page 672 - Engineering Digital Design

P. 672

640 CHAPTER 13 / ALTERNATIVE SYNCHRONOUS FSM ARCHITECTURES

a(L)

D

e(H) = Z(H) H >-H . Q |—H e(H) = Z(H)

Sanity(L) CK Sanity(L)

(a) (b)

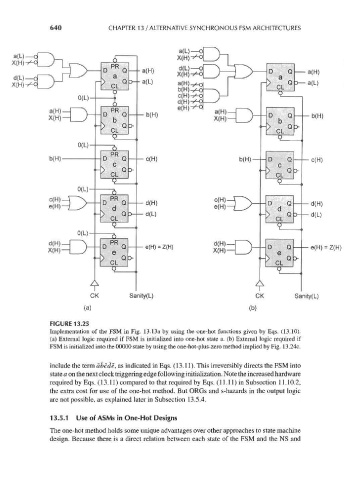

FIGURE 13.25

Implementation of the FSM in Fig. 13.13a by using the one-hot functions given by Eqs. (13.10).

(a) External logic required if FSM is initialized into one-hot state a. (b) External logic required if

FSM is initialized into the 00000 state by using the one-hot-plus-zero method implied by Fig. 13.24c.

include the term abode, as indicated in Eqs. (13.11). This irreversibly directs the FSM into

state a on the next clock triggering edge following initialization. Note the increased hardware

required by Eqs. (13.11) compared to that required by Eqs. (11.11) in Subsection 11.10.2,

the extra cost for use of the one-hot method. But ORGs and s-hazards in the output logic

are not possible, as explained later in Subsection 13.5.4.

13.5.1 Use of ASMs in One-Hot Designs

The one-hot method holds some unique advantages over other approaches to state machine

design. Because there is a direct relation between each state of the FSM and the NS and