Page 109 - System on Package_ Miniaturization of the Entire System

P. 109

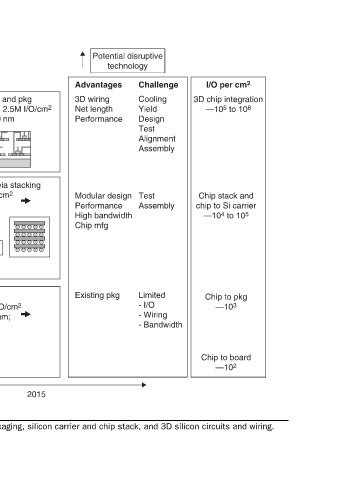

I/O per cm 2 3D chip integration —10 5 to 10 8 Chip stack and chip to Si carrier —10 4 to 10 5 Chip to pkg —10 3 Chip to board —10 2

Potential disruptive technology Challenge Advantages Cooling 3D wiring Yield Net length Design Performance Test Alignment Assembly Test Modular design Assembly Performance High bandwidth Chip mfg Limited Existing pkg - I/O - Wiring - Bandwidth

3D Si integration and pkg - I/O: 6-mm pitch; 2.5M I/O/cm 2 - Wiring pitch: 90 nm Si carrier pkg and through-via stacking - I/O: 50-μm pitch; 40K I/O/cm 2 Chip 2 Substrate BGA, CGA, or LGA Ceramic and organic pkg - I/O: 150-mm pitch; 4K I/O/cm 2 - Wiring pitch: MLC 150 mm; 2015 2010 A silicon integration comparison for ceramic and organic

3D integration - Wiring pitch: 2 mm Chip 1 SLC 40 mm 2005 Year

Si carrier and chip stacking - I/O: 200-mm pitch; 2.5K I/O/cm 2

Organic and ceramic pkg (SCM and MCM) Ceramic and organic pkg - Wiring pitch: MLC 200 mm; SLC 50 mm Printed circuit card 2000

FIGURE 3.2 (Courtesy of IBM) [1]

Integration

84