Page 121 - System on Package_ Miniaturization of the Entire System

P. 121

96 Cha pte r T h ree

A new generation of chip stacking began to evolve in the 1990s. It is stacking of bare

chips leading to higher stacking density. The electrical performance was also greatly

enhanced by employing short interconnections that include wire bonding, tape

automated bonding (TAB), or newly introduced side termination methods. Even though

the wire bonding technology had been used since the 1970s, it was only in the 1990s

when the technology began to be applied to SIP on a commercial scale. A few package

stackings were also demonstrated by employing the same configuration as chip stacking

with side termination interconnects.

The wire bonded chip stacking interconnection led to the introduction of flip chip

interconnection for SIP around 2000 when flip chip became a high-volume assembly

technology. Application of embedded IC technology to chip stacking enabled chip-scale

package (CSP) stacking. At about this time, some of the limitations of chip stacking

technologies were also realized. This led to alternatives to chip stacking, which include

package-on-package (PoP), package-in-package (PiP) and folded-stacked chip scale

package (FSCSP).

The following two sections describe widely used non-TSV chip and package

stacking technologies currently in use.

3.3.2 Chip Stacking

Over the past few years, chip stacking has emerged as an effective solution for integrating

similar or dissimilar chips. Integrating chips vertically in a single package multiplies

the amount of silicon that can be crammed in a given package footprint, conserving

board real estate. At the same time, it enables shorter routing of interconnects from chip

to chip, which speeds signaling between them. Initial applications of chip stacking were

two-chip memory combinations such as flash and SRAM. Memory stacking remains

the most popular even today but includes new variations like flash plus flash. More

recently, it has been further extended beyond memories to include the combination of

logic and analog ICs. In this section, various chip stacking architectures are introduced

with the basic underlying technologies for their chip stacking.

Wafer Thinning, Handling, and Dicing

Advances in chip stacking technologies are enabling the stacking of more dies in a given

height. To accomplish this basic goal, a variety of underlying technologies have been

developed, which include wafer thinning, thin wafer handling, and dicing as described

here.

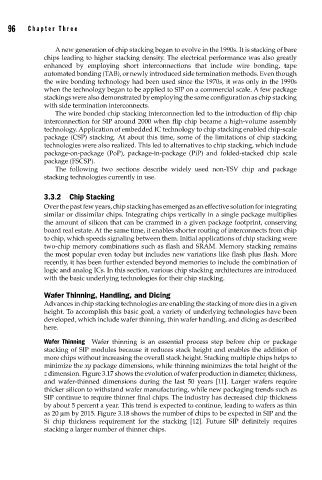

Wafer Thinning Wafer thinning is an essential process step before chip or package

stacking of SIP modules because it reduces stack height and enables the addition of

more chips without increasing the overall stack height. Stacking multiple chips helps to

minimize the xy package dimensions, while thinning minimizes the total height of the

z dimension. Figure 3.17 shows the evolution of wafer production in diameter, thickness,

and wafer-thinned dimensions during the last 50 years [11]. Larger wafers require

thicker silicon to withstand wafer manufacturing, while new packaging trends such as

SIP continue to require thinner final chips. The industry has decreased chip thickness

by about 5 percent a year. This trend is expected to continue, leading to wafers as thin

as 20 μm by 2015. Figure 3.18 shows the number of chips to be expected in SIP and the

Si chip thickness requirement for the stacking [12]. Future SIP definitely requires

stacking a larger number of thinner chips.