Page 96 - System on Package_ Miniaturization of the Entire System

P. 96

72 Cha pte r T w o

IP-1 IP-2 . . .

Hierarchical SOC

Glue logic Abstractions SOC

Design planning

Partitioning assembly

Prototyping

Block

implementation

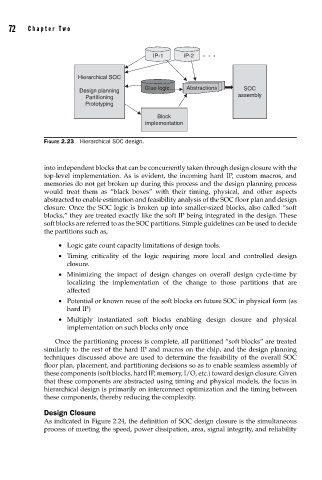

FIGURE 2.23 Hierarchical SOC design.

into independent blocks that can be concurrently taken through design closure with the

top-level implementation. As is evident, the incoming hard IP, custom macros, and

memories do not get broken up during this process and the design planning process

would treat them as “black boxes” with their timing, physical, and other aspects

abstracted to enable estimation and feasibility analysis of the SOC floor plan and design

closure. Once the SOC logic is broken up into smaller-sized blocks, also called “soft

blocks,” they are treated exactly like the soft IP being integrated in the design. These

soft blocks are referred to as the SOC partitions. Simple guidelines can be used to decide

the partitions such as,

• Logic gate count capacity limitations of design tools.

• Timing criticality of the logic requiring more local and controlled design

closure.

• Minimizing the impact of design changes on overall design cycle-time by

localizing the implementation of the change to those partitions that are

affected

• Potential or known reuse of the soft blocks on future SOC in physical form (as

hard IP)

• Multiply instantiated soft blocks enabling design closure and physical

implementation on such blocks only once

Once the partitioning process is complete, all partitioned “soft blocks” are treated

similarly to the rest of the hard IP and macros on the chip, and the design planning

techniques discussed above are used to determine the feasibility of the overall SOC

floor plan, placement, and partitioning decisions so as to enable seamless assembly of

these components (soft blocks, hard IP, memory, I/O, etc.) toward design closure. Given

that these components are abstracted using timing and physical models, the focus in

hierarchical design is primarily on interconnect optimization and the timing between

these components, thereby reducing the complexity.

Design Closure

As indicated in Figure 2.24, the definition of SOC design closure is the simultaneous

process of meeting the speed, power dissipation, area, signal integrity, and reliability