Page 92 - System on Package_ Miniaturization of the Entire System

P. 92

68 Cha pte r T w o

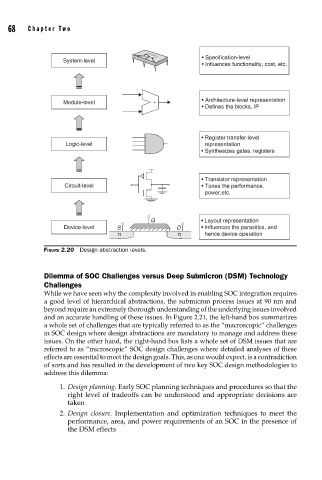

• Specification-level

System-level

• Influences functionality, cost, etc.

Module-level + • Architecture-level representation

• Defines the blocks, IP

• Register transfer-level

Logic-level representation

• Synthesizes gates, registers

• Transistor representation

Circuit-level • Tunes the performance,

power,etc.

G • Layout representation

Device-level S D • Influences the parasitics, and

n n hence device operation

FIGURE 2.20 Design abstraction levels.

Dilemma of SOC Challenges versus Deep Submicron (DSM) Technology

Challenges

While we have seen why the complexity involved in enabling SOC integration requires

a good level of hierarchical abstractions, the submicron process issues at 90 nm and

beyond require an extremely thorough understanding of the underlying issues involved

and an accurate handling of these issues. In Figure 2.21, the left-hand box summarizes

a whole set of challenges that are typically referred to as the “macroscopic” challenges

in SOC design where design abstractions are mandatory to manage and address these

issues. On the other hand, the right-hand box lists a whole set of DSM issues that are

referred to as “microscopic” SOC design challenges where detailed analyses of these

effects are essential to meet the design goals. This, as one would expect, is a contradiction

of sorts and has resulted in the development of two key SOC design methodologies to

address this dilemma:

1. Design planning. Early SOC planning techniques and procedures so that the

right level of tradeoffs can be understood and appropriate decisions are

taken

2. Design closure. Implementation and optimization techniques to meet the

performance, area, and power requirements of an SOC in the presence of

the DSM effects