Page 276 - Sami Franssila Introduction to Microfabrication

P. 276

25

CMOS Transistor Fabrication

CMOS remains the most voluminous microfabricated lithography and etching, plus the source/drain diffusions.

device by a wide margin. Many of the process steps of Contact defines the division between the front end and

microfabrication were developed originally for CMOS the back end: after the metal–silicon interface has been

fabrication, and later adapted to other microdevices. formed, process temperatures become limited to ca.

◦

In the last 30 years, linewidth scaling has been driven 450 C. The number of metallization levels has increased

almost exclusively by CMOS. Ion implantation was steadily: 5 µm CMOS had one level, 2 µm CMOS two

a technique for high-resolution nuclear spectroscopy levels, 0.8 µm CMOS three levels and with 0.13 µm

in the 1960s, but today CMOS doping is its main generation has seven levels of metal.

application. Thin oxides, down to 2 nm today, are really

nanostructures in volume production, and major CMOS

wafer fabs produce these oxides by square metres a day. 25.1 5 µm POLYSILICON GATE CMOS PROCESS

CMOS linewidths were in the 5 µm range in the mid

1970s. This may sound like old-fashioned technology, Process integration begins with wafer selection. n-type

but it was the time when CMOS got its present-day silicon, 4 ohm-cm (phosphorus concentration ca. 1.5 ×

−3

15

appearance and diverged dramatically from older gen- 10 cm ) is chosen as the starting material. This will

eration aluminium gate processes. The 5 µm process mean that NMOS transistors will be made in p-well, and

exhibits most of the essential process steps that char- PMOS transistors in the substrate directly. The choice

acterize CMOS: it is an oxide-isolated, ion-implanted, of p-type starting material would lead to a reversed

plasma-etched, self-aligned gate process (Table 25.1). configuration.

Advanced CMOS features and processes will be dis- In Figure 25.2, the top view of the photomask is

cussed later in this chapter after the basic polygate pro- shown, together with a cross-sectional view of the device

cess has been presented. at a specified stage of the process.

The main modules of CMOS fabrication are shown Wafers are cleaned, and a pad oxide of 40 nm is

in Figure 25.1. Front end is about diffusions and doping grown in dry oxygen and followed by LPCVD nitride

profiles. It is high-temperature processing. The gate deposition (100 nm). These films will be used in making

module involves gate oxidation and gate poly deposition, the LOCOS isolation structure. The first lithography

step defines transistor-active areas. Nitride will cover

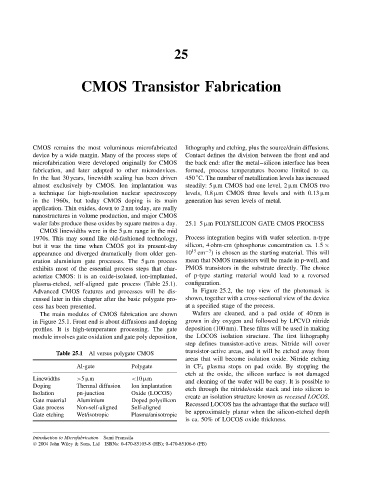

Table 25.1 Al versus polygate CMOS transistor-active areas, and it will be etched away from

areas that will become isolation oxide. Nitride etching

Al-gate Polygate in CF 4 plasma stops on pad oxide. By stopping the

etch at the oxide, the silicon surface is not damaged

Linewidths >5 µm <10 µm and cleaning of the wafer will be easy. It is possible to

Doping Thermal diffusion Ion implantation

etch through the nitride/oxide stack and into silicon to

Isolation pn-junction Oxide (LOCOS) create an isolation structure known as recessed LOCOS.

Gate material Aluminium Doped polysilicon

Recessed LOCOS has the advantage that the surface will

Gate process Non-self-aligned Self-aligned

Gate etching Wet/isotropic Plasma/anisotropic be approximately planar when the silicon-etched depth

is ca. 50% of LOCOS oxide thickness.

Introduction to Microfabrication Sami Franssila

2004 John Wiley & Sons, Ltd ISBNs: 0-470-85105-8 (HB); 0-470-85106-6 (PB)