Page 558 - DSP Integrated Circuits

P. 558

12.3 Layout Styles 543

EXAMPLE 12.1

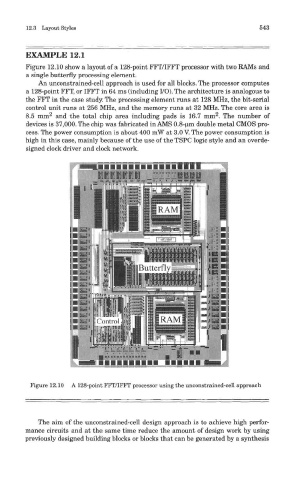

Figure 12.10 show a layout of a 128-point FFT/IFFT processor with two RAMs and

a single butterfly processing element.

An unconstrained-cell approach is used for all blocks. The processor computes

a 128-point FFT, or IFFT in 64 ms (including I/O). The architecture is analogous to

the FFT in the case study. The processing element runs at 128 MHz, the bit-serial

control unit runs at 256 MHz, and the memory runs at 32 MHz. The core area is

2

2

8.5 mm and the total chip area including pads is 16.7 mm . The number of

devices is 37,000. The chip was fabricated in AMS 0.8-um double metal CMOS pro-

cess. The power consumption is about 400 mW at 3.0 V. The power consumption is

high in this case, mainly because of the use of the TSPC logic style and an overde-

signed clock driver and clock network.

Figure 12.10 A 128-point FFT/IFFT processor using the unconstrained-cell approach

The aim of the unconstrained-cell design approach is to achieve high perfor-

mance circuits and at the same time reduce the amount of design work by using

previously designed building blocks or blocks that can be generated by a synthesis