Page 562 - DSP Integrated Circuits

P. 562

12.5 DCT PROCESSOR, Cont. 547

12.5 DCT PROCESSOR, CONT.

Two sets of memories are required for the DCT processor, since two images are

processed concurrently. Each memory is implemented as two dual-port RAMs with

128 x 16-bits. The size of one such RAM is

^RAM = 0.7 x 1.3 = 0.9 mm 2

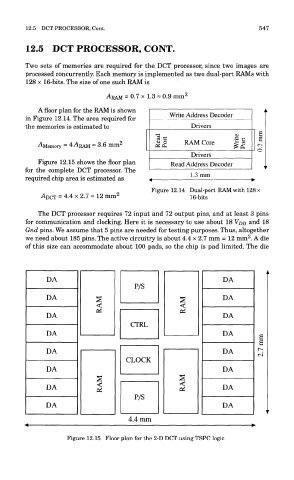

A floor plan for the RAM is shown

in Figure 12.14. The area required for

the memories is estimated to

•^Memory = 4 ARAM ~ 3.6 mm 2

Figure 12.15 shows the floor plan

for the complete DCT processor. The

required chip area is estimated as

Figure 12.14 Dual-port RAM with 128 x

2

A DCT = 4.4 x 2.7 * 12 mm 16-bits

The DCT processor requires 72 input and 72 output pins, and at least 3 pins

for communication and clocking. Here it is necessary to use about 18 VDD and 18

Gnd pins. We assume that 5 pins are needed for testing purposes. Thus, altogether

2

we need about 185 pins. The active circuitry is about 4.4 x 2.7 mm = 12 mm . A die

of this size can accommodate about 100 pads, so the chip is pad limited. The die

Figure 12.15 Floor plan for the 2-D DCT using TSPC logic