Page 173 - Embedded Microprocessor Systems Real World Design

P. 173

I 1

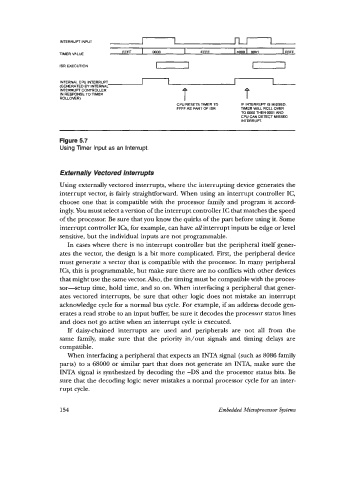

INTERRUPT INPUT

FFFF I aoao I FFFF laowl 0001 I FFFF

TIMER VALUE

0 0

ISR EXECUTION

I I I I

INTERNAL CPU INTERRUPT

(GENERATED BY INTERNAL

INTERRUPT CONTROLLER f

IN RESPONSE TOTIMER f

ROLLOMR)

CW RESETS TIMER TO IF INTERRUPT IS MISSED.

FFFF AS PART OF ISR TIMER WILL ROLL OMR

TO OOM) THEN ooO1 AND

CW CAN DETECT MISSED

INTERRUPT.

Figure 5.7

Using Timer Input as an Interrupt.

Externally Vectored Interrupts

Using externally vectored interrupts, where the interrupting device generates the

interrupt vector, is fairly straightforward. When using an interrupt controller IC,

choose one that is compatible with the processor family and program it accord-

ingly. You must select a version of the interrupt controller IC that matches the speed

of the processor. Be sure that you know the quirks of the part before using it. Some

interrupt controller ICs, for example, can have allinterrupt inputs be edge or level

sensitive, but the individual inputs are not programmable.

In cases where there is no interrupt controller but the peripheral itself gener-

ates the vector, the design is a bit more complicated. First, the peripheral device

must generate a vector that is compatible with the processor. In many peripheral

ICs, this is programmable, but make sure there are no conflicts with other devices

that might use the same vector. Also, the timing must be compatible with the proces

sor-tup time, hold time, and so on. When interfacing a peripheral that gener-

ates vectored interrupts, be sure that other logic does not mistake an interrupt

acknowledge cycle for a normal bus cycle. For example, if an address decode gen-

erates a read strobe to an input buffer, be sure it decodes the processor status lines

and does not go active when an interrupt cycle is executed.

If daisy-chained interrupts are used and peripherals are not all from the

same family, make sure that the priority in/out signals and timing delays are

compatible.

When interfacing a peripheral that expects an INTA signal (such as 8086 family

parts) to a 68000 or similar part that does not generate an INTA, make sure the

INTA signal is synthesized by decoding the -DS and the processor status bits. Be

sure that the decoding logic never mistakes a normal processor cycle for an inter-

rupt cycle.

154 Ernbedded Mimoprocessar Systems