Page 371 - Embedded Microprocessor Systems Real World Design

P. 371

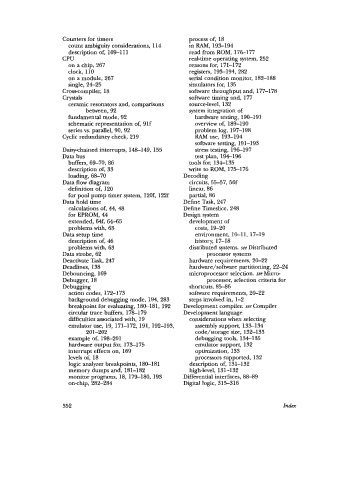

Counters for timers process of, 18

count ambiguity considerations, 114 in RAM, 193-194

description of, 109-111 read from ROM, 1761 77

CPU real-time operating system, 252

on a chip, 267 reasons for, 171-172

clock, 110 registers, 193-194, 282

on a module, 267 serial condition monitor, 182-188

single, 2425 simulators for, 135

Crosscompiler, 18 software throughput and, 177-178

Crystals software timing and, 177

ceramic resonators and, comparisons source-level, 132

between, 92 system integration of

fundamental mode, 92 hardware testing, 190-191

schematic representation of, 91f overview of, 189-190

series vs. parallel, 90,92 problem log, 197-198

Cyclic redundancy check, 219 RAM use, 193-194

software testing, 191-193

Daisychained interrupts, 148-149, 155 stress testing, 196-197

Data bus test plan, 194-196

buffers, 69-70,86 tools for, 134-135

description of, 33 write to ROM, 175-176

loading, 68-70 Decoding

Data flow diagram circuits, 55-57, 56f

definition of, 120 linear, 86

for pool pump timer system, 120f, 122f partial, 86

Data hold time Define Task, 247

calculations of, 44, 48 Define Timeslice, 248

for EPROM, 44 Design system

extended, 64, 64-65 development of

problems with, 63 costs, 19-20

Data setup time environment, 10-11, 17-19

description of, 46 history, 17-18

problems with, 63 distributed systems. see Distributed

Data strobe, 62 processor systems

Deactivate Task, 247 hardware requirements, 20-22

Deadlines, 138 hardware/software partitioning, 22-24

Debouncing, 169 microprocessor selection. see Micro-

Debugger, 18 processor, selection criteria for

Debugging shortcuts, 85-86

action codes, 172-1 73 software requirements, 20-22

background debugging mode, 194,283 steps involved in, 1-2

breakpoint for evaluating, 180-181, 192 Development compiler. see Compiler

circular trace buffers, 178-179 Development language

difficulties associated with, 19 considerations when selecting

emulator use, 19, 171-172, 191,192-193, assembly support, 133-134

201-202 code/storage size, 132-133

example of, 198-201 debugging tools, 134-135

hardware output for, 173-1 75 emulator support, 132

interrupt effects on, 169 optimization, 133

levels of, 18 processors supported, 132

logic analyzer breakpoints, 180-181 description of, 131-132

memory dumps and, 181-182 high-level, 131-1 32

monitor programs, 18, 179-180, 193 Differential interfaces, 88-89

onchip, 282-284 Digital logic, 315-316

352 Index