Page 301 - Engineering Digital Design

P. 301

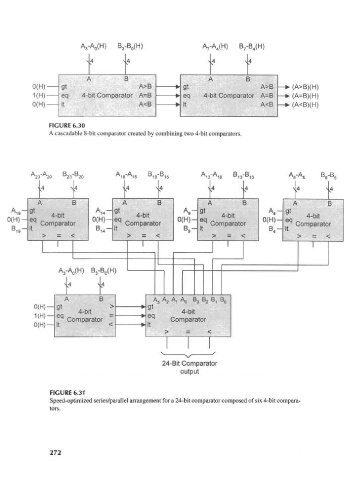

A 3-A 0(H) B 3-B 0(H) A 7-A 4(H) B 7-B 4(H)

\ 4 > A N 4 v 4

X\ I3 {•^ 13

0(H) gt A>B *> gt A>B (A>B)(H)

I ^ n^ """ eq 4-bit Comparator A=B 4-bit Comparator A=B (A=B)(H)

A I II \ > eq

0(H) It A<B *> It A<B (A<B)(H)

FIGURE 6.30

A cascadable 8-bit comparator created by combining two 4-bit comparators.

A A B B A A B B A A B B A A B B

23~ 20 23~ 20 18~ 15 18~ 15 13~ 10 13~ 10 8~ 5 8~ 5

4

A B A B A B

gt A 14- gt 9~ gt A.- gt

A A

19 4-bit 4-bit

0(H)- eq 4-bit 0(H)- 0(H)- 0(H)- eq 4-bit

Comparator Comparator Comparator Comparator

it o*. —It B 0- it B,- it

'14

> = < > = <

A 3-A 0(H) B 3-B 0(H)

u >u

A B A 3 A 2 A, AO B 3 B 2 B, B 0

0(H) — gt -fr- gt

4-bit 4-bit

Comparator Comparator

0(H) — It

24-Bit Comparator

output

FIGURE 6.31

Speed-optimized series/parallel arrangement for a 24-bit comparator composed of six 4-bit compara-

tors.

272