Page 396 - Engineering Digital Design

P. 396

8.8 ARITHMETIC AND LOGIC UNITS 367

B A B A

n-1 n-1 . . . B 2 A 2 B 1 A 1 o o

(H) (H) (H) (H) (H) (H) (H) (H)

1 /P/U|\

D(H)-4<

rr/Lj\ 4x

c-\n ) — / '

4 ' \-\ ' 4 X ' 4, ' 4, ' t «,- \ ' 4,' 4 4 -4, '

/

t: D B A E: D B A EE D B A E: [) B A

R R R I— R

L/R —I L/R —I L/R —I UR —I

... EN

LSB

C nout(L) <-C '-'out ""*• n-i *^in o+- «: Co,,< PALU 2 C jn O«-C C m)) PALU, C jn cx-c C out PALU 0 C tn r^^t p

u

J

^~ ,.~m

(L)

MSB C ->C c in C out D->- ->C Cm c out D->C c fn c ou, D-^C c in c out

(L) '"

-C EN -C EN rC EN -C EN

Y Y Y Y Y Y Y Y

<f Y <P Y

EN(L) 1

F,i(H) F 2(H) F^H) F 0(H)

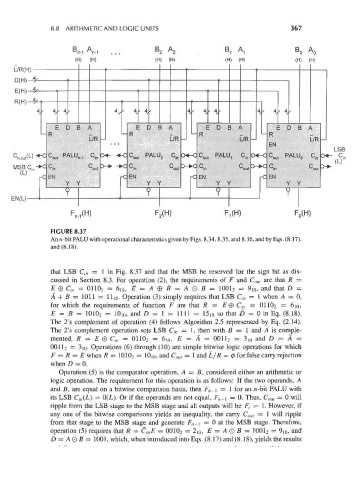

FIGURE 8.37

An rc-bit PALU with operational characteristics given by Figs. 8.34, 8.35, and 8.36, and by Eqs. (8.17).

and (8.18).

that LSB C in = 1 in Fig. 8.37 and that the MSB be reserved for the sign bit as dis-

cussed in Section 8.3. For operation (2), the requirements of F and C ollt are that R =

E © C in = 01102 = 610, E = A®B = AQB = 1001 2 = 9i 0, and that D =

A + B = 1011 = 1110. Operation (3) simply requires that LSB C in = I when A = 0,

for which the requirements of function F are that R = E © C- m = 01102 = 610,

E = B = 1010 2 = lOio, and D = 1 = 1111 = 15i 0 so that D = 0 in Eq. (8.18).

The 2's complement of operation (4) follows Algorithm 2.5 represented by Eq. (2.14).

The 2's complement operation sets LSB C- m = 1, then with B = 1 and A is comple-

mented, R = E © C in = 0110 2 = 610, E = A = 0011 2 = 3 m and D = A =

00112 = 310- Operations (6) through (10) are simple bitwise logic operations for which

F = R = E when R = 1010 2 = lOio, and C out = 1 and L/R = 0 for false carry rejection

when D = 0.

Operation (5) is the comparator operation, A = B, considered either an arithmetic or

logic operation. The requirement for this operation is as follows: If the two operands, A

and B, are equal on a bitwise comparison basis, then F,,_i = 1 for an n-bit PALU with

its LSB C in(L) = 0(L). Or if the operands are not equal, F n-\ = 0. Thus, C out = 0 will

ripple from the LSB stage to the MSB stage and all outputs will be F { = 1. However, if

any one of the bitwise comparisons yields an inequality, the carry C out = 1 will ripple

from that stage to the MSB stage and generate F n-\ = 0 at the MSB stage. Therefore,

operation (5) requires that R = C inE = 0010 2 = 2i 0 , E = A O B = 1001 2 = 9io, and

D = A Q B = 1001, which, when introduced into Eqs. (8.17) and (8.18), yields the results