Page 564 - Engineering Digital Design

P. 564

534 CHAPTER 11 /SYNCHRONOUS FSM DESIGN CONSIDERATIONS

Sanity

Action blocks

(b)

(a)

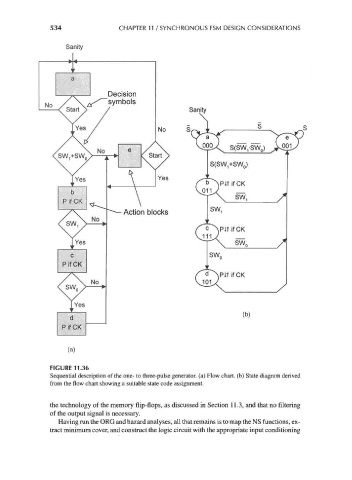

FIGURE 11.36

Sequential description of the one- to three-pulse generator, (a) Flow chart, (b) State diagram derived

from the flow chart showing a suitable state code assignment.

the technology of the memory flip-flops, as discussed in Section 11.3, and that no filtering

of the output signal is necessary.

Having run the ORG and hazard analyses, all that remains is to map the NS functions, ex-

tract minimum cover, and construct the logic circuit with the appropriate input conditioning