Page 601 - Engineering Digital Design

P. 601

Pj(H)

Qj-i(H)

Universal Shift

Register

Q A Q B Q c Q 0

CL(L) '

Qj(H) (b)

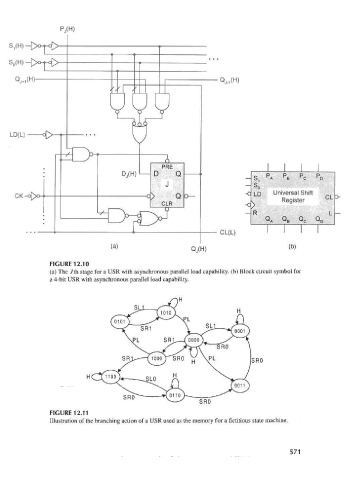

FIGURE 12.10

(a) The Jth stage for a USR with asynchronous parallel load capability, (b) Block circuit symbol for

a 4-bit USR with asynchronous parallel load capability.

SRO

SR

° ^ ' SRO

FIGURE 12.11

Illustration of the branching action of a USR used as the memory for a fictitious state machine.

571