Page 250 - A Practical Guide from Design Planning to Manufacturing

P. 250

222 Chapter Seven

flip-flop, signal B (SigB), to switch. This must happen before the rise of

clock signal B (ClkB) 1 cycle after the rise of ClkA. The amount the SigB

is earlier than needed is the maxdelay timing margin.

In addition to requiring a maximum delay for each pipestage, there

is also a need for a minimum delay. A very fast pipestage might allow

its signals to pass through and reach the next flip-flop before it has

closed. This would allow the signals to pass through two flip-flops in

1 cycle and would end with them in the wrong pipestage. Like cars

crashing into one another, the proper data from one pipestage would be

lost when it was overtaken from behind by the signals from the previ-

ous pipestage. The main function of flip-flops is to stop speeding signals

from entering the next pipestage too soon, keeping the signals of each

pipestage separate. A circuit that has so little delay that its data could

jump ahead to the wrong pipestage is said to have a mindelay violation

or a race.

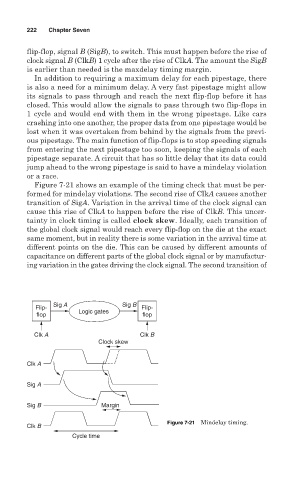

Figure 7-21 shows an example of the timing check that must be per-

formed for mindelay violations. The second rise of ClkA causes another

transition of SigA. Variation in the arrival time of the clock signal can

cause this rise of ClkA to happen before the rise of ClkB. This uncer-

tainty in clock timing is called clock skew. Ideally, each transition of

the global clock signal would reach every flip-flop on the die at the exact

same moment, but in reality there is some variation in the arrival time at

different points on the die. This can be caused by different amounts of

capacitance on different parts of the global clock signal or by manufactur-

ing variation in the gates driving the clock signal. The second transition of

Sig A Sig B

Flip- Flip-

Logic gates

flop flop

Clk A Clk B

Clock skew

Clk A

Sig A

Sig B Margin

Figure 7-21 Mindelay timing.

Clk B

Cycle time